Le microprocesseur 6809 et kit JHL68B09

Il s'agit ici de reconstituer une version modernisée d'un système informatique à base de 6809 construit dans les années 70.

Modernisée en ce sens qu'à l'époque, par mesure d'économie, la RAM utilisée était dynamique et donc nécessitait un système de rafraichissement.

Nous utiliserons une RAM statique. RAM et ROM occuperont tout l'espace possible de 64Ko du 68B09. Avec la limitation de la taille ROM à 32K. Taille (ROM) + Taille (RAM) = 64Ko

Modernisée aussi car, les signaux de sélection des composants seront issus d'un GAL au lieu de nombreux composants discrets de la famille 74LS...

Modernisée aussi car, les signaux de sélection des composants seront issus d'un GAL au lieu de nombreux composants discrets de la famille 74LS...

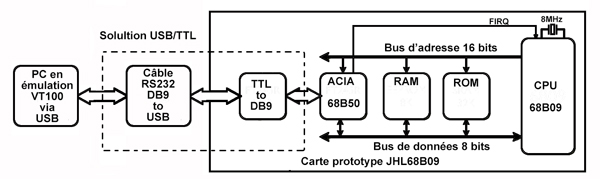

Le synoptique du prototype

La technologie retenue est du type 68Bxx. Elle permet de faire travailler le CPU à 8MHZ, soit deux fois la fréquence du composant de base.

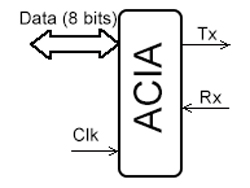

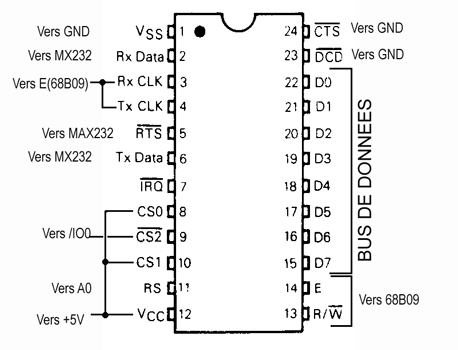

Le prototype est conçu avec un seul composant d'entrée/sortie: l'ACIA 68B50. Il s'agit d'un contrôleur de communication série asynchrone. Il permettait de

de communiquer avec un terminal (TTY) de type VT100 ou autre. Ce composants transforme les données binaires, composées de mots de 8bits, en un signal porté

par un seul fil. Les 8 bits étant émis les uns à la suite des autres (en série). Ce principe sera décrit plus loin.

La communication avec ce type de terminal se faisait selon une norme physique nommée RS232. Dans cette norme, les 0 et 1 binaires se présentent sous la forme de tensions de -12V et +12V.

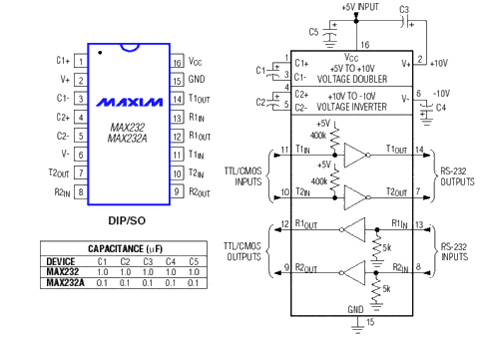

Aujourd'hui, il devient difficile de trouver ce type de terminal. On pourra utiliser un PC converti logiciellement en Terminal VT100 mais communiquant via son port USB. Dans les années 70, la conversion TTL (coté ACIA) vers RS232 (coté terminal) nécessitait une alimentation de ±12V en plus de l'alimentation électrique de 5V TTL. Les composants historiques de conversion étaient souvent le couple (MC1488 et MC1489). Aujourd'hui, les composants de conversion intègre un convertisseur 5/±12V comme le MAX232. Donc, plus besoin d'une alimentation supplémentaire de ±12V.

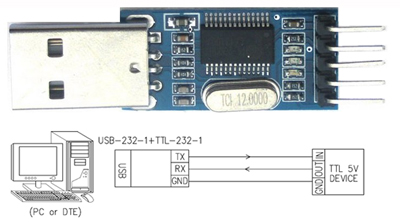

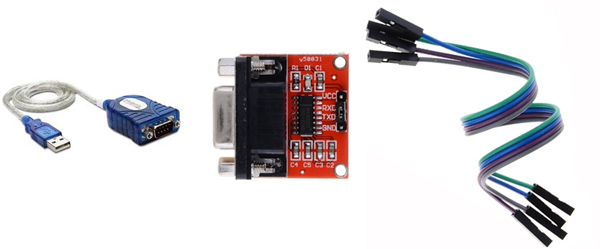

Conversion TTL Série / USB

Aujourd'hui, la conversion TTL/RS232/USB sera assurée par un circuit qui effectue toute la chaîne de conversion. On trouve dans le commerce, de petit module bon marché

assurant cette conversion.

IL faut ajouter à cela l'installation d'un device driver sur le PC, faisant «croire» à celui-ci qu'il communique via un port série RS232. On pourra choisir de bien distinguer la conversion TTL/RS232 et RS232/USB. C'est l'option retenue ici.

IL faut ajouter à cela l'installation d'un device driver sur le PC, faisant «croire» à celui-ci qu'il communique via un port série RS232. On pourra choisir de bien distinguer la conversion TTL/RS232 et RS232/USB. C'est l'option retenue ici.

Sérialisation

Cet opération est assurée par des composants appelés ACIA, USART, UART.

L'Acia 68B50 est un sérialiseur. C'est à dire, qu'il transforme un mot de 8 bits émis en parallèle. sur le bus de donnée nommé Data sur la figure ci-contre en une série de bits

transmis sur le fil nommé Tx. Les bits sont émis au rythme de l'horloge Clk.

A l'inverse, un signal de la même nature reçu sur Rx sera recomposé sur le bus Data.

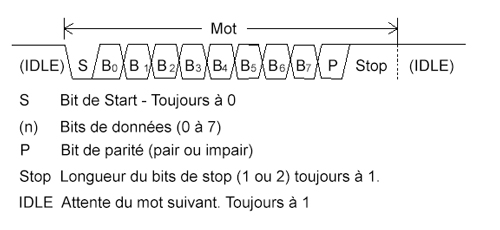

La synchronisation des échanges est assurée par un bit de START et un bit de STOP entre les bits de données sérialisés sur Tx et Rx.

A l'inverse, un signal de la même nature reçu sur Rx sera recomposé sur le bus Data.

La synchronisation des échanges est assurée par un bit de START et un bit de STOP entre les bits de données sérialisés sur Tx et Rx.

Les bits non obligatoires sont :

- P (pas de contrôle de parité)

- B7 ( les mots émis sont codés sut 7 bits).

- la durée du bit de stop.

- la taille du mot (7 ou 8 bits).

- la présence d'un bit de parité et sa nature (odd ou even).

- la fréquence d'émission en baud (bit/seconde) sous la forme d'une division de FClk /4 puis par 16 ou 64. Fbaud= FClk /(64 | 256).

- 110 baud

- 300 baud

- 1 200 baud

- 2 400 baud

- 4 800 baud

- 9 600 baud

- 19 200 baud

- 38 400 baud

- 57 600 baud

- 115 200 baud (10 500 octets/s)

La fréquence de communication choisie pour le prototype sera de 115 200 baud. L'horloge sera issue du signal E du CPU qui en théorie est de fréquence 8MHZ.

Dans ce cas le rapport F(E)/F(baud) est 8 000 000/ 115 200 = 69.4.

Cette division étant devant être assurée par l'Acia et ne pouvant prendre que les valeurs 64 ou 256, il faudrait que F(E) soit égale à 64 x 115 200 = 7 372 800 Hz.>br /> Avec ue division par 256, on obtient une communication à 28 800 baud.

Le quartz qui cadence le CPU sera un 7,3728MHz et non un 8MHz. A cette cadence, un écran de 80 colonnes x 24 lignes est affiché en 0.18 s.

Cette division étant devant être assurée par l'Acia et ne pouvant prendre que les valeurs 64 ou 256, il faudrait que F(E) soit égale à 64 x 115 200 = 7 372 800 Hz.>br /> Avec ue division par 256, on obtient une communication à 28 800 baud.

Le quartz qui cadence le CPU sera un 7,3728MHz et non un 8MHz. A cette cadence, un écran de 80 colonnes x 24 lignes est affiché en 0.18 s.

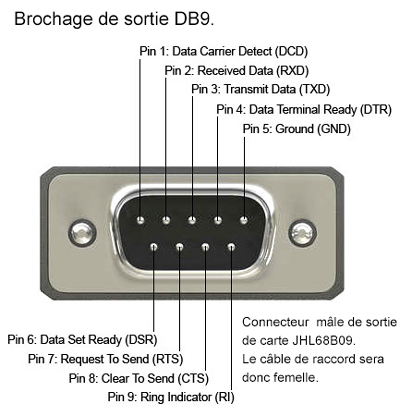

Norme RS232

On trouvera un article Wikipédia sur le sujet ici .

Elle porte sur

Elle porte sur

- les niveaux électriques des signaux binaires (0/1). Avec 0 ==> +V et 1 ==> -V). V étant compris entre 3 et 15V.

- des signaux de contrôle additionnels permettant de réguler le débit des données.

- le câblage des connecteurs DB25 ou DB9 portant les signaux.

| DB9 | DB25 | Signal | Nom | Direction |

|---|---|---|---|---|

| 1 | 8 | DCD | Data Carrier Detect | In |

| 2 | 3 | RXD | Receive Data | In |

| 3 | 2 | TXD | Transmit Data | Out |

| 4 | 20 | DTR | Data Terminal Ready | Out |

| 5 | 7 | GND | Ground | - |

| 6 | 6 | DSR | Data Set Ready | In |

| 7 | 4 | RTS | Request to Send | Out |

| 8 | 5 | CTS | Clear to Send | In |

| 9 | 22 | RI | Ring Indicator | In |

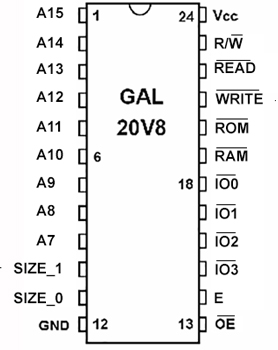

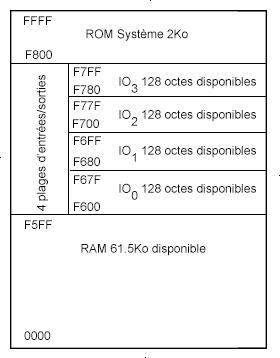

Cartographie mémoire

Cette cartographie est gérée via un circuit GAL 20V8, dont les broches sont fixées comme ci-contre.

Les broches (SIZE_1, SIZE_0) permettent de choisir la cartographie.

(*) RAM SIZE = 64KB - 0.5KB - ROM SIZE

Les étendues des espaces ROM, RAM et IO sont

Les broches (SIZE_1, SIZE_0) permettent de choisir la cartographie.

| SIZE_1 | SIZE_0 | ROM SIZE | IO SIZE | RAM SIZE * |

| 0 | 0 | 2KB | 512B | 61.5KB |

| 0 | 1 | 4KB | 512B | 59.5KB |

| 1 | 0 | 8KB | 512B | 55.5KB |

| 1 | 1 | 16KB | 512B | 47.5KB |

(*) RAM SIZE = 64KB - 0.5KB - ROM SIZE

Les étendues des espaces ROM, RAM et IO sont

| ROM SIZE | IO SIZE | RAM SIZE * | RAM RANGE | IO RANGE | ROM RANGE |

| 2KB | 512B | 61.5KB | 0000 - F5FF | F600 - F7FF | F800 - FFF |

| 4KB | 512B | 59.5KB | 0000 - EDFF | EE00 - EFFF | F000 - FFF |

| 8KB | 512B | 55.5KB | 0000 - DDFF | DE00 - DFFF | E000 - FFF |

| 16KB | 512B | 47.5KB | 0000 - BDFF | BE00 - BFFF | C000 - FFF |

Programmation du GAL

L'espace IO de 512 octets est divisé en 4 sous-espace de 128 octets (I00 à IO3).

On trouvera ici le fichier JED pour la programmation du GAL

Un extrait du code VHDL ayant permit la programmation du GAL est donné ci-dessous. le code complet est téléchargeable ici.

On trouvera ici le fichier JED pour la programmation du GAL

Un extrait du code VHDL ayant permit la programmation du GAL est donné ci-dessous. le code complet est téléchargeable ici.

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity test1 is

port(A : in std_logic_vector(15 downto 7);

SIZE: in std_logic_vector(1 downto 0);

E : in std_logic;

RW : in std_logic;

RAM, ROM, IO0, IO1, IO2, IO3, READ, WRITE : out std_logic);

ATTRIBUTE LOC : string;

-- Inputs

ATTRIBUTE LOC OF A : SIGNAL IS "1 2 3 4 5 6 7 8 9";

ATTRIBUTE LOC OF E : SIGNAL IS "14";

ATTRIBUTE LOC OF RW : SIGNAL IS "23";

ATTRIBUTE LOC OF SIZE : SIGNAL IS "10 11";

-- Outputs

ATTRIBUTE LOC OF READ : SIGNAL IS "22";

ATTRIBUTE LOC OF WRITE : SIGNAL IS "21";

ATTRIBUTE LOC OF ROM : SIGNAL IS "20";

ATTRIBUTE LOC OF RAM : SIGNAL IS "19";

ATTRIBUTE LOC OF IO0 : SIGNAL IS "18";

ATTRIBUTE LOC OF IO1 : SIGNAL IS "17";

ATTRIBUTE LOC OF IO2 : SIGNAL IS "16";

ATTRIBUTE LOC OF IO3 : SIGNAL IS "15";

end;

architecture test1 of test1 is

begin

process(SIZE)

variable IO : std_logic := '0';

begin

case SIZE is

-- ROM de 2Ko

when "00" =>

ROM <= not (A(15) and A(14) and A(13) and A(12) and A(11));

IO := A(15) and A(14) and A(13) and A(12) and not A(11) and A(10) and A(9);

when "01" =>

ROM <= not (A(15) and A(14) and A(13) and A(12));

IO := A(15) and A(14) and A(13) and not A(12) and A(11) and A(10) and A(9) ;

when "10" =>

ROM <= not (A(15) and A(14) and A(13));

IO := not A(15) and A(14) and A(13) and A(12) and A(12) and A(11) and A(9);

when "11" =>

ROM <= not (A(15) and A(14));

IO := A(15) and not A(14) and A(13) and A(12) and A(11) and A(10) and A(9);

end case;

IO0 <= not (IO and not A(8) and not A(7));

IO1 <= not (IO and not A(8) and A(7));

IO2 <= not (IO and A(8) and not A(7));

IO3 <= not (IO and A(8) and A(7));

RAM <= not(ROM) or not(IO); -- to /CS of RAM

WRITE <= not(E and not(RW)); -- to /WE of RAM

READ <= not(E and RW); -- to /CE of ROM

end process;

end test1;

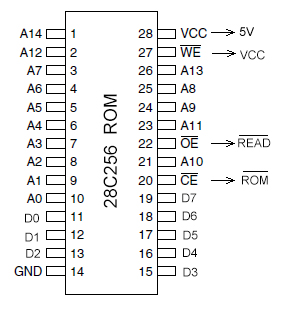

ROM

Le composant ROM choisi est une EEPROM ATMEL AT28C256-15PU / DIP-28 d'une capacité de 32,768 mots de 8 bits. Programmable et effaçable électriquement.

Dans la version du prototype actuel, seuls 2, 4 , 8 ou 16K seront utilisés. Ce choix pourra varier dans le future.

Les signaux /READ, /ROM sont issus du circuit GAL.

Pour la première mise en œuvre, la configuration ROM sera minimale : 2Ko.pour cela les entrées de GAL (SIZE_1, SIZE_0) = (0,0). L'ACIA sera sélectionné par le signal /IO0.

Les signaux /READ, /ROM sont issus du circuit GAL.

Pour la première mise en œuvre, la configuration ROM sera minimale : 2Ko.pour cela les entrées de GAL (SIZE_1, SIZE_0) = (0,0). L'ACIA sera sélectionné par le signal /IO0.

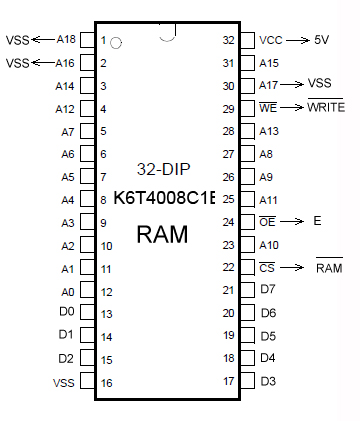

RAM

La RAM statique choisie est une K6T4008C1B-DL70 / DIP-32 d'une capacité de 512 Koctets.Seuls 64Ko seront utlisés (les bits A18, A17 et A16 seront forcés à 0).

Les signaux /WRITE, /RAM sont issus du circuit GAL. E st issu du CPU 68B09.

Les signaux /WRITE, /RAM sont issus du circuit GAL. E st issu du CPU 68B09.

ACIA (USART)

Le composant ACIA